TSMC의 북미 기술 심포지엄에서 회사는 수요일에 반도체 기술과 칩 패키징 기술 로드맵을 상세히 설명했습니다. 전자는 Moore의 법칙의 전통적인 부분을 유지하는 데 중요하며, 후자는 점점 더 많은 실리콘으로 제작된 프로세서로의 추세를 가속화할 수 있으며, 빠르게 전체 실리콘 웨이퍼 크기의 시스템으로 이어질 수 있습니다. TSMC에 따르면, 테슬라의 다음 세대 도조 트레이닝 타일은 이미 생산 중입니다. 그리고 2027년에는 이 발견소가 테슬라의 것보다 더 복잡한 웨이퍼 스케일 시스템에 기술을 제공할 계획이며, 이 시스템은 오늘날의 시스템보다 40배 더 많은 컴퓨팅 파워를 제공할 수 있습니다.

개요

수십 년 동안 칩 제조업체는 주로 트랜지스터가 차지하는 영역과 인터커넥션의 크기를 축소함으로써 프로세서에서 논리의 밀도를 증가시켰습니다. 그러나 그 방식은 이미 한동안 효과가 줄어들고 있습니다. 대신, 산업은 하나의 프로세서를 더 많은 실리콘으로 제작할 수 있는 고급 패키징 기술을 채택하고 있습니다. 단일 칩의 크기는 리소그라피 장비가 만들 수 있는 가장 큰 패턴에 제한됩니다. 현재 약 800 제곱 밀리미터입니다. 따라서 GPU에 더 많은 실리콘을 원한다면 두 개 이상의 다이에서 만들어야 합니다. 핵심은 그 다이를 연결하여 신호가 하나의 큰 실리콘 조각인 것처럼 빠르고 적은 에너지로 다른 다이로 이동할 수 있도록 하는 것입니다.

TSMC는 이미 Cerebras를 위한 웨이퍼 크기의 AI 가속기를 생산하고 있지만, 이 배치는 독특한 것으로 보이며, TSMC가 지금 제공하는 시스템 온 웨이퍼라고 하는 것과 다릅니다.

Cerebras를 위해 TSMC는 리소그라피 한도보다 작은 AI 코어의 동일한 어레이로 가득 찬 웨이퍼를 만듭니다. 이들 어레이를 “scribe lines”를 통해 연결하여, 일반적으로 공백으로 남겨져 있는 다이 사이의 영역으로 웨이퍼를 칩으로 나눌 수 있습니다. 어떤 칩 제조 공정도 완벽하지 않기 때문에, 모든 웨이퍼에는 항상 결함이 있는 부분이 있습니다. 그러나 Cerebras는 충분한 중복성을 디자인하여 완성된 컴퓨터에는 중요하지 않습니다.

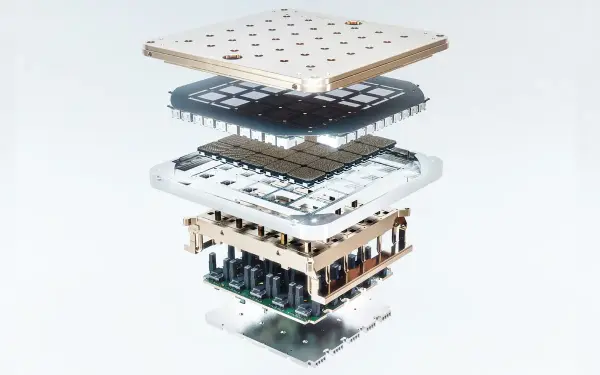

그러나, 첫 번째 라운드의 System-on-Wafer에서 TSMC는 리소그라피 한도와 수율의 문제에 대한 다른 해결책을 제공하고 있습니다. 결함을 최소화하기 위해 이미 테스트된 로직 다이를 시작점으로 삼습니다. (테슬라의 Dojo는 사전 테스트된 프로세서의 5×5 그리드를 포함합니다.) 이들은 캐리어 웨이퍼 위에 배치되며, 다이 사이의 공백은 채워집니다. 그런 다음 TSMC의 통합 팬-아웃 기술을 사용하여 로직을 연결하기 위해 고밀도 인터커넥트 레이어가 구축됩니다. 목표는 다이 사이의 데이터 대역폭을 높여서 실제로 하나의 큰 칩처럼 작동할 수 있도록 하는 것입니다.

2027년까지, TSMC는 보다 고급스러운 패키징 기술인 칩-온-웨이퍼-온-서브스트레이트(CoWoS)를 기반으로 웨이퍼 스케일 통합을 제공할 계획입니다. 이 기술에서는 사전 테스트된 로직과 중요한 고대역폭 메모리가, 고밀도 인터커넥트로 패턴화된 실리콘 서브스트레이트에 부착되며, 수직 연결인 씨스루 실리콘 비아를 통해 삽입됩니다. 부착된 로직 칩은 또한 회사의 시스템-온-통합 칩(SoIC)이라고 불리는 3D 칩 기술을 활용할 수 있습니다.

CoWoS의 웨이퍼 스케일 버전은 이미 최고급 GPU에서 확인할 수 있는 패키징 기술의 확장의 논리적인 종점입니다. Nvidia의 다음 GPU인 Blackwell은 CoWoS를 사용하여 3개 이상의 리소그라피 크기의 실리콘과 8개의 고대역폭 메모리(HBM) 칩을 통합합니다. 회사는 2026년까지 이를 5.5개의 리소그라피, 12개의 HBM을 포함하여 확장할 계획입니다. TSMC는 이것이 그들의 2023 기술보다 3.5배 이상의 컴퓨팅 파워로 변환될 것이라고 말합니다. 그러나 2027년에는 실리콘 웨이퍼의 40배 이상의 컴퓨팅을 제공하는 전체 웨이퍼 통합이 가능할 것으로 TSMC는 예측합니다.

웨이퍼 레벨에서의 제작이 좋은 점

2027년판 시스템 온 웨이퍼는 UCLA에서 5년 전에 개발된 Silicon-Interconnect Fabric(Si-IF) 또는 Si-IF라는 기술과 약간 닮았습니다. SiIF를 개발한 팀에는 전기 및 컴퓨터 공학 교수 Puneet Gupta와 지금은 미국 CHIPS Act의 패키징 부분을 구현하는 것을 담당하고 있는 IEEE 펠로우인 Subramanian Iyer가 포함되어 있습니다.

이후, 그들은 웨이퍼의 인터커넥트를 더 밀도 있게 만들고 기술에 다른 기능을 추가하기 위해 노력해왔습니다. “만약 이것을 완전한 기술 인프라로 원한다면, 그것은 단순히 미세한 피치 연결성을 제공하는 것 이상의 다른 많은 일들을 해야 합니다,”라고 말합니다. “이러한 대규모 시스템에서 가장 큰 고민거리 중 하나는 전력을 공급하는 것입니다.” 따라서 UCLA 팀은 실리콘 기판에 우수한 품질의 캐패시터 및 인덕터를 추가하고 샐리움 질화물 전력 트랜지스터를 통합하는 방법에 대해 연구하고 있습니다.

AI 훈련은 웨이퍼 스케일 기술에 대한 명백한 첫 번째 응용 프로그램이지만, 유일한 것은 아니며, 심지어 최상의 것일 수도 없습니다. 일리노이 대학 어배나-샴페인 캠퍼스의 컴퓨터 아키텍트이자 IEEE 펠로우 인 Rakesh Kumar는 말합니다. 6월에 열리는 국제 컴퓨터 아키텍처 심포지엄에서 그의 팀은 데이터 센터용 웨이퍼 스케일 네트워크 스위치 디자인을 발표할 예정입니다. 연구원들에 따르면, 이러한 시스템은 매우 큰(16,000랙) 데이터 센터에서 고급 네트워크 스위치의 수를 4,608개에서 48개로 줄일 수 있습니다. 8,000대 서버용으로는 웨이퍼 스케일 스위치 하나만으로도 충분한 훨씬 작은 기업용 데이터 센터가 될 수 있습니다.

정리

이번 포스팅에서는 웨이퍼 스케일 기술의 현재 발전 상황과 미래 전망에 대해 논의하였습니다. AI 훈련을 비롯한 다양한 응용 분야에서 웨이퍼 스케일 기술이 적용될 수 있음을 살펴보았으며, 이를 통해 데이터 센터 및 기업 환경에서의 효율성 향상 가능성을 엿보았습니다. 또한, 다양한 연구와 개발 노력이 웨이퍼 스케일 기술의 확장과 적용을 뒷받침하고 있음을 보여주었습니다. 앞으로 이 기술이 어떻게 발전하고 새로운 산업 분야에 적용될지 기대해 봅니다.